Funktionsbaustein

Level-1

- Beiträge

- 69

- Reaktionspunkte

- 2

-> Hier kostenlos registrieren

guten morgen SPS Welt!

ich moechte fuer eine Aufgabe ein Datenbit seriell verschieben und 4 ausgaenge parallel abfragen.

die perfekte loesung waere ein 4 bit Schieberegister mit einem seriellen Dateninput und 4 parallelen ausgaenge.

zb

aber in twicat 3 gibt es nicht (so ein baustein), soweit ich weiss. kann man ein solcher Baustein bauen? wenn ja, wie?

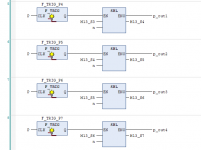

ich habe folgendes gemacht:

- 4 Netzwerk , in dem ich 4 baustein SHL mit EN/ENO eingebaut habe. dann ein fallende Taktimpuls P (EN) , Eingang D (zu verschieben), n=1(zahl der bit zu verschieben), D1 (ausgang) und P_out(ENO) wurde am ersten baustein angehängt. bei den 3 folgenden Netzwerke habe ich D1/D2, D2/D3, D3/D4 als EIngang/ Ausgang gemacht. Ausgangspostion p=True und D=1 danach kann D beliebige werte annehmen 0 der 1. Aber während der Simulation ist mein Ergebnis falsch.

was habe ich falsch gemacht?

koennte jmd mir sagen wie ich das loesen soll? mit FBD-sprache

danke im voraus fuer ihre Hilfe

ich moechte fuer eine Aufgabe ein Datenbit seriell verschieben und 4 ausgaenge parallel abfragen.

die perfekte loesung waere ein 4 bit Schieberegister mit einem seriellen Dateninput und 4 parallelen ausgaenge.

zb

aber in twicat 3 gibt es nicht (so ein baustein), soweit ich weiss. kann man ein solcher Baustein bauen? wenn ja, wie?

ich habe folgendes gemacht:

- 4 Netzwerk , in dem ich 4 baustein SHL mit EN/ENO eingebaut habe. dann ein fallende Taktimpuls P (EN) , Eingang D (zu verschieben), n=1(zahl der bit zu verschieben), D1 (ausgang) und P_out(ENO) wurde am ersten baustein angehängt. bei den 3 folgenden Netzwerke habe ich D1/D2, D2/D3, D3/D4 als EIngang/ Ausgang gemacht. Ausgangspostion p=True und D=1 danach kann D beliebige werte annehmen 0 der 1. Aber während der Simulation ist mein Ergebnis falsch.

was habe ich falsch gemacht?

koennte jmd mir sagen wie ich das loesen soll? mit FBD-sprache

danke im voraus fuer ihre Hilfe

Zuletzt bearbeitet: