larry

Level-2

- Beiträge

- 59

- Reaktionspunkte

- 1

-> Hier kostenlos registrieren

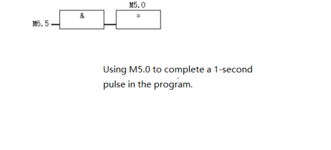

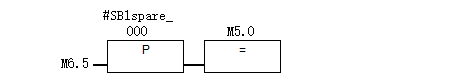

What's the best way to generate a 1s pulse in a PLC program? The first way is to use a clock memory with rising edge instructions, and the second way involves using logic instructions like AND, OR, and NOT to handle the clock memory. I'm using STEP7.